# NATIONAL STRATEGY ON MICROELECTRONICS RESEARCH

A Report by the SUBCOMMITTEE ON MICROELECTRONICS LEADERSHIP COMMITTEE ON HOMELAND AND NATIONAL SECURITY

of the

NATIONAL SCIENCE AND TECHNOLOGY COUNCIL

### **About the Office of Science and Technology Policy**

The Office of Science and Technology Policy (OSTP) was established by the National Science and Technology Policy, Organization, and Priorities Act of 1976 to provide the President and others within the Executive Office of the President with advice on the scientific, engineering, and technological aspects of the economy, national security, homeland security, health, foreign relations, the environment, and the technological recovery and use of resources, among other topics. OSTP leads interagency science and technology policy coordination efforts, assists the Office of Management and Budget (OMB) with an annual review and analysis of federal research and development in budgets, and serves as a source of scientific and technological analysis and judgment for the President with respect to major policies, plans, and programs of the federal government. More information is available at <a href="https://www.whitehouse.gov/ostp/nstc">www.whitehouse.gov/ostp/nstc</a>.

#### **About the National Science and Technology Council**

The National Science and Technology Council (NSTC) is the principal means by which the Executive Branch coordinates science and technology policy across the diverse entities that make up the federal research and development enterprise. A primary objective of the NSTC is to ensure that science and technology policy decisions are consistent with the President's stated goals. The NSTC prepares research and development strategies that are coordinated across federal agencies aimed at accomplishing multiple national goals. The work of the NSTC is organized under committees that oversee subcommittees and working groups focused on different aspects of science and technology. More information is available at <a href="https://www.whitehouse.gov/ostp/nstc">www.whitehouse.gov/ostp/nstc</a>.

### **About the Subcommittee on Microelectronics Leadership**

The Subcommittee on Microelectronics Leadership (SML) of the NSTC was established pursuant to Section 9906 of the William M. (Mac) Thornberry National Defense Authorization Act for Fiscal Year 2021 (Public Law 116-283), Title XCIX. SML coordinates activities across the Executive Branch of the federal government related to U.S. leadership and competitiveness in microelectronics technology and innovation. SML is also helping to coordinate Executive Branch implementation of the CHIPS Act of 2022 (Division A of Public Law 117-167) with the broader whole-of-government effort to grow the nation's semiconductor manufacturing base and accelerate microelectronics research and development (R&D), including activities by agencies not funded specifically to perform additional semiconductor/microelectronics R&D under the CHIPS Act of 2022 (e.g., the National Science Foundation, the Department of Energy, and the Defense Advanced Research Projects Agency).

#### **About this document**

This document is the National Strategy on Microelectronics Research called for in Section 9906 of Public Law (P.L.) 116-283, Title XCIX. This strategy identifies four goals to guide agency efforts in microelectronics research to (a) accelerate the domestic development and production of microelectronics and strengthen the domestic microelectronics workforce; and (b) ensure that the United States remains a global leader in the field of microelectronics R&D. In addition to input from the many agencies represented on SML, it reflects extensive consultation with the Industrial Advisory Committee established under P.L. 116-283 as well as other stakeholders from industry, non-governmental organizations, and academia.

#### **Disclaimer**

Reference in this report to any product, service, enterprise, or individual, including any written works (i.e., books, articles, papers) is not an endorsement and does not imply official U.S. government sanction or endorsement of those entities or their views. Links to non-U.S. government websites do not constitute or imply official U.S. government or OSTP endorsement of or responsibility for the opinions, ideas, data, or products presented at those locations, or guarantee the validity of the information provided.

### **Copyright information**

This document is a work of the United States government and is in the public domain (see 17 USC §105). Subject to stipulations below, it may be distributed and copied, with acknowledgement to OSTP. Copyrights to graphics included in this document are reserved by original copyright holders or their assignees and are used here under the government's license and by permission. Requests to use any images must be made to the provider identified in the image credits, or to OSTP if no provider is identified.

Published in the United States of America, 2024.

#### NATIONAL SCIENCE AND TECHNOLOGY COUNCIL

**Chair:** Arati Prabhakar, Assistant to the President for Science and Technology; Director, White House Office of Science and Technology Policy

Acting Executive Director: Kei Koizumi, Principal Deputy Director for Policy, Office of Science and Technology Policy

#### SUBCOMMITTEE ON MICROELECTRONICS LEADERSHIP (SML)

**SML Co-Chairs:**

Jason Boehm, DOC Lisa Friedersdorf, OSTP Carl McCants, DOD SML Executive Secretary:

Corey Stambaugh, NIST

#### SUBCOMMITTEE ON MICROELECTRONICS LEADERSHIP PARTICIPANTS

### Office of Science and Technology Policy (OSTP)

Lisa Friedersdorf Dana Weinstein

**National Economic Council (NEC)**

Peter Devine

**National Security Council (NSC)**

Nikita Lalwani

Office of Management and Budget (OMB)

Nancy Kenly William McNavage

Office of the U.S. Trade Representative (USTR)

Rebecca Gudicello

National Coordination Office for Networking and Information Technology R&D (NITRD)

Craig Schlenoff

National Nanotechnology Coordination Office (NNCO)

Branden Brough Quinn Spadola

National Quantum Coordination Office (NQCO)

Charles Tahan

**Department of Commerce (DOC)**

**International Trade Administration (ITA)**

Paul Litwin Luke Myers

National Institute of Standards and Technology (NIST)

Jason Boehm

**Richard-Duane Chambers**

David Gundlach

J. Alexander Liddle

Eric Lin

Robert Rudnitsky

Department of Defense (DOD)

Carl McCants

Alison Smith

**Devanand Shenoy**

**Department of Energy (DOE)**

Hal Finkel

**Andrew Schwartz**

Department of Health and Human Services (HHS)

**National Institutes of Health (NIH)**

David Rampulla

**Department of Homeland Security (DHS)**

Jalal Mapar

Pauline Paki

#### **Department of State (State)**

Kakoli Ray Michael Masuda Elizabeth Melenbrink Scott Sellars

### **National Science Foundation (NSF)**

Dilma Da Silva Erwin Gianchandani Germano Iannacchione Barry Johnson Anthony A. Maciejewski

# Office of the Director of National Intelligence (ODNI)

John Beieler Eric Cheng Donald Parrish

### **Table of Contents**

| Abbreviations and Acronyms                                                                                                                         | V     |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Executive Summary                                                                                                                                  | vi    |

| Introduction                                                                                                                                       | 1     |

| The Microelectronics Innovation Ecosystem                                                                                                          | 7     |

| A Whole-of-Government Approach                                                                                                                     | 10    |

| Goal 1. Enable and Accelerate Research Advances for Future Generations of Microelectronics                                                         | 11    |

| 1.1: Accelerate the research and development of materials that provide new capabilities or functional enhancements.                                | 15    |

| 1.2: Increase the capabilities of circuit design, simulation, and emulation tools                                                                  | 16    |

| 1.3: Develop a diverse array of robust processing architectures and associated hardware needed for future systems.                                 | 16    |

| 1.4: Develop processes and metrology for advanced packaging and heterogeneous integration                                                          | n 17  |

| 1.5: Prioritize hardware integrity and security as an element in co-design strategies across the stack                                             | 18    |

| 1.6: Invest in R&D for manufacturing tools and processes needed to support transition of innovations into production-worthy fabrication processes. | 19    |

| Goal 2. Support, Build, and Bridge Microelectronics Infrastructure from Research to Manufacturi                                                    | ng 21 |

| 2.1: Support federated networks of device-scale R&D fabrication and characterization user facilities.                                              | 22    |

| 2.2: Improve access for the academic and small-business research community to flexible design tools and wafer-scale fabrication resources.         | 24    |

| 2.3: Facilitate research access to key functional materials.                                                                                       | 25    |

| 2.4: Expand access to advanced cyberinfrastructure for modeling and simulation                                                                     | 25    |

| 2.5: Support advanced research, development, and prototyping to bridge the lab-to-fab gap                                                          | 26    |

| 2.6: Support advanced assembly, packaging, and testing                                                                                             | 29    |

| Goal 3. Grow and Sustain the Technical Workforce for the Microelectronics R&D to Manufacturing Ecosystem                                           | 30    |

| 3.1: Support learners and educators in and across science and technology disciplines relevant to microelectronics                                  | 32    |

| 3.2: Foster meaningful public engagement in microelectronics and raise awareness of career opportunities in the semiconductor industry             | 34    |

| 3.3: Prepare an inclusive current and future microelectronics workforce                                                                            | 35    |

| 3.4. Build and drive microelectronics research and innovation capacity                                                                             | 37    |

#### NATIONAL STRATEGY ON MICROELECTRONICS RESEARCH

| Goal 4. Create a Vibrant Microelectronics Innovation Ecosystem to Accelerate the Transition of R&D to U.S. Industry                                                       | .39  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.1: Support, build, and bridge centers, public private partnerships, and consortia to deepen collaboration among various stakeholders in the microelectronics ecosystem. | . 40 |

| 4.2: Engage with and leverage the CHIPS Industrial Advisory Committee.                                                                                                    | .44  |

| 4.3: Motivate and align the microelectronics community on key technical challenges with R&D roadmaps and grand challenges                                                 | . 45 |

| 4.4: Facilitate academic, government, and industrial exchange to broaden understanding of needs and opportunities.                                                        | . 46 |

| 4.5: Support entrepreneurship, start-ups, and early-stage businesses through targeted programs and investments                                                            | . 46 |

| Advancing Research and Development to Support Manufacturing and Supply Chain Security                                                                                     | .49  |

| International Collaboration and the Role of Trade and Diplomacy                                                                                                           | .49  |

| Future Directions                                                                                                                                                         | .51  |

### Abbreviations and Acronyms<sup>1</sup>

ML

machine learning

| 2D      | two-dimensional                                                              | MSI                                   | minority-serving institution                                            |

|---------|------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------|

| 3D      | three-dimensional                                                            | NASA                                  | National Aeronautics and Space                                          |

| 3DHI    | 3D heterogeneous integration                                                 |                                       | Administration                                                          |

| ADK     | assembly design kit                                                          | NGMM                                  | Next-Generation Microsystems                                            |

| Al      | artificial intelligence                                                      |                                       | Manufacturing (DARPA program)                                           |

| CHIPS   | Creating Helpful Incentives to Produce                                       | nm                                    | nanometer                                                               |

|         | Semiconductors (abbreviation for P.L. 116-283, Title XCIX, and Division A of | NNCI                                  | National Nanotechnology Coordinated<br>Infrastructure (NSF program)     |

|         | P.L. 117-167)                                                                | NNI                                   | National Nanotechnology Initiative                                      |

| CMOS    | complementary metal-oxide-<br>semiconductor                                  | NSTC                                  | National Semiconductor Technology<br>Center (also, National Science and |

| DARPA   | Defense Advanced Research Projects                                           |                                       | Technology Council)                                                     |

|         | Agency                                                                       | OECD                                  | Organisation for Economic Co-                                           |

| DTCO    | design-technology co-optimization                                            |                                       | operation and Development                                               |

| EDA     | electronic design automation                                                 | OSTP                                  | Office of Science and Technology Policy                                 |

| ENIAC   | Electronic Numerical Integrator and                                          | PDK                                   | process design kit                                                      |

|         | Computer                                                                     | RFI                                   | Request for Information                                                 |

| FFRDC   | Federally Funded Research and                                                | R&D                                   | research and development                                                |

|         | Development Center                                                           | Si                                    | silicon                                                                 |

| FLOPS   | floating-point operations per second                                         | STCO                                  | system technology co-optimization                                       |

| HBCU(s) | Historically Black Colleges and Universities                                 | STEM                                  | science, technology, engineering, and mathematics                       |

| IP      | intellectual property                                                        | TCCU Tribally Controlled Colleges and | Tribally Controlled Colleges and                                        |

| KSAs    | knowledge, skills, and abilities                                             |                                       | Universities                                                            |

| MEMS    | microelectromechanical systems                                               |                                       |                                                                         |

| MGI     | Materials Genome Initiative                                                  |                                       |                                                                         |

|         |                                                                              |                                       |                                                                         |

See the Subcommittee on Microelectronics Leadership roster (pp. i-ii) for spelling out of acronyms of participating agency names.

### **Executive Summary**

Decades ago, American innovation sparked the research advances that led to the semiconductor industry of today. This industry is global, underpins everything from health to communications, and is essential for the economy and security of the United States. The significant investments made possible by the bipartisan CHIPS Acts provide opportunities to reinvigorate domestic manufacturing in this critical sector, and strengthen the microelectronics research and development (R&D) innovation ecosystem that can advance the American competitive position for the future.

This National Strategy on Microelectronics Research presents goals, key needs, and actions required over the next five years to realize these opportunities. This strategy provides the framework for federal departments and agencies, academia, industry, nonprofits, and international allies and partners to address key needs and build out the microelectronics research and development infrastructure to support the future advances that will shape the semiconductor field.

As highlighted throughout this report, the significant CHIPS R&D investments underway must be fully leveraged and coordinated with the broad portfolio of ongoing programs, activities, and resources that contribute to microelectronics research and development. Over the next five years, the White House and federal departments and agencies will work together to advance four interconnected goals:

- Enable and Accelerate Research Advances for Future Generations of Microelectronics

- Support, Build, and Bridge Microelectronics Infrastructure from Research to Manufacturing

- Grow and Sustain the Technical Workforce for the Microelectronics Research and Development to Manufacturing Ecosystem

- Create a Vibrant Microelectronics Innovation Ecosystem to Accelerate the Transition of Research and Development to U.S. Industry

The first goal focuses on key research needs in several areas that are required to accelerate the advances required for future generations of microelectronic systems. Research areas include materials that can provide new capabilities; circuit design, simulation, and emulation tools; new architectures and associated hardware designs; processes and metrology for advanced packaging and heterogeneous integration; hardware integrity and security; and manufacturing tools and processes to enable transition of new innovations into production.

These research areas require access to specialized tools and equipment. The second goal is focused on supporting, expanding, and connecting the research infrastructure from small-scale material and device-level fabrication and characterization through prototyping, large-scale fabrication, and advanced assembly, packaging, and testing. The required tools include both software (including design tools) and commercial-scale production and metrology hardware.

Expansion of the domestic semiconductor industry will also expand opportunities for good-paying jobs across the country. Goal three identifies efforts to support learners and educators in the development of the technical workforce required from research through manufacturing.

Finally, goal four is focused on the entire R&D landscape and presents strategies and actions to create a vibrant microelectronics innovation ecosystem to accelerate the transition of new advances into commercial applications. Key efforts not only support actions at each stage of the microelectronics technology development pathway, but also connect the various networks and activities to build a virtuous cycle of microelectronics innovation.

#### NATIONAL STRATEGY ON MICROELECTRONICS RESEARCH

These four goals will be pursued in the context of the global nature of the semiconductor industry. As is the case with the semiconductor manufacturing supply chain, research facilities and talent that support the microelectronics innovation ecosystem are located all over the world. International collaboration, trade, and diplomacy are important tools to leverage efforts and resources, promote talent flow and research collaboration, and ensure secure supply chains.

Implementation of this strategy will result in a vibrant innovation ecosystem that accelerates new research breakthroughs, supports the transition of these advances to manufacturing, and provides good-paying jobs to people all across America. A fully built-out and well-connected microelectronics research infrastructure will provide the foundation for researchers to advance their breakthroughs and lead to a virtuous innovation cycle. Nurturing and supporting microelectronics innovation will help secure future leadership in the semiconductor industry for the security and prosperity of the United States and its allies and partners.

#### Introduction

The microelectronics<sup>2</sup> revolution has transformed society. Nearly all aspects of modern life are now dependent on semiconductor technology, including communications, computing, entertainment, health care, energy, and transportation. As a result, microelectronics are essential to the economic and national security of the United States. Rapid innovation in the semiconductor industry has been fueled for decades by research and development (R&D) investments in hardware and software by the federal government and the private sector.<sup>3</sup>

The intense race to continually increase the performance and functionality of microelectronics, while maintaining or reducing cost and power requirements, has driven the fabrication of ever smaller and more densely integrated microelectronic components. This miniaturization has required continuous breakthroughs in materials, tools, and design that have enabled key structures within the components to have dimensions as small as a few atoms in size. While reductions in feature size have led to dramatic increases in digital information storage and processing capacity, there have also been many significant advances in analog and non-silicon technologies that are critical for communications, power, and sensing. The required advances in manufacturing have been enabled by significant investments not only in R&D, but also in developing the manufacturing and metrology equipment and the associated fabrication ("fabs") and packaging facilities required to make advanced integrated circuits and components. The complexity and cost of manufacturing at this scale—establishing a leading-edge<sup>4</sup> silicon fab complex now costs tens of billions of dollars<sup>5</sup>—has contributed to significant consolidation in the industry. Today, only three corporations in the world are competing to manufacture the latest generations of advanced logic devices.<sup>6</sup>

In June 2021, the White House released *Building Resilient Supply Chains, Revitalizing American Manufacturing, and Fostering Broad-Based Growth*, a report on critical supply chains, including the semiconductor manufacturing and advanced packaging supply chain.<sup>7</sup> The report noted that although U.S.-headquartered semiconductor companies accounted for nearly half of worldwide revenue, the share of global semiconductor manufacturing conducted domestically had dropped from 37% in 1990 to 12%, and the U.S. share of packaging had fallen to 3%.<sup>8</sup> As discussed in the report, modern

Microelectronics in this context refers to integrated electronic devices and systems generally manufactured using semiconductor-based materials and related processing (i.e., in a semiconductor fabrication manufacturing facility, or "fab"). Such devices and systems include analog and digital electronics, power electronics, optics and photonics, and micromechanics for memory, processing, sensing, and communications applications.

<sup>&</sup>lt;sup>3</sup> The semiconductor industry refers to the manufacturing sector including design and production of products consisting of semiconductor-based electronic devices and integrated circuits, along with advanced packaging and power electronics.

<sup>&</sup>quot;Leading-edge" refers to the most miniaturized or "scaled" digital computing and memory technology—currently denoted the "3 nm node"—with new, smaller nodes being produced every two to three years.

For example, see, TSMC looks to double down on U.S. chip factories as talks in Europe falter, https://www.globalbankingandfinance.com/exclusive-tsmc-looks-to-double-down-on-u-s-chip-factories-as-talks-in-europe-falter; and Intel: Upcoming U.S. Fab Will Be a Small City, to Cost \$60 to \$120 Billion, https://www.tomshardware.com/news/intel-to-spend-up-to-120-billion-on-new-us-manufacturing-hub.

See, The Semiconductor Supply Chain: Assessing National Competitiveness, <a href="https://cset.georgetown.edu/wp-content/uploads/The-Semiconductor-Supply-Chain-Issue-Brief.pdf">https://cset.georgetown.edu/wp-content/uploads/The-Semiconductor-Supply-Chain-Issue-Brief.pdf</a>.

Building Resilient Supply Chains, Revitalizing American Manufacturing, and Fostering Broad-Based Growth, The White House, 2021, <a href="https://www.whitehouse.gov/wp-content/uploads/2021/06/100-day-supply-chain-review-report.pdf">https://www.whitehouse.gov/wp-content/uploads/2021/06/100-day-supply-chain-review-report.pdf</a>. Note: This initial report did not include power electronics or other specialized semiconductors for clean energy applications such as photovoltaics (PVs), which were addressed in follow-on reports: <a href="https://www.energy.gov/policy/securing-americas-clean-energy-supply-chain">https://www.energy.gov/policy/securing-americas-clean-energy-supply-chain</a>.

The U.S. share of global assembly, test, and packaging is now estimated to be less than 2%: <a href="https://www.bis.doc.gov/index.php/documents/technology-evaluation/3402-section-9904-report-final-20231221/file.">https://www.bis.doc.gov/index.php/documents/technology-evaluation/3402-section-9904-report-final-20231221/file.</a>

microelectronics manufacturing is an incredibly complex and global process, involving hundreds of steps completed over several months, with many components using international expertise and facilities as they traverse the world several times. The report concluded that the public and private sectors need to act to increase domestic manufacturing capacity for critical goods, recruit and train a domestic workforce, invest in R&D, and work with America's allies and partners to collectively strengthen supply chain resilience.

#### National Strategy on Microelectronics Research—Goals and Objectives

#### Goal 1. Enable and Accelerate Research Advances for Future Generations of Microelectronics

- 1.1: Accelerate the research and development of materials that provide new capabilities or functional enhancements.

- 1.2: Increase the capabilities of circuit design, simulation, and emulation tools.

- 1.3: Develop a diverse array of robust processing architectures and associated hardware needed for future systems.

- 1.4: Develop processes and metrology for advanced packaging and heterogeneous integration.

- 1.5: Prioritize hardware integrity and security as an element in co-design strategies across the stack.

- 1.6: Invest in R&D for manufacturing tools and processes needed to support transition of innovations into production-worthy fabrication processes.

#### Goal 2. Support, Build, and Bridge Microelectronics Infrastructure from Research to Manufacturing

- 2.1: Support federated networks of device-scale R&D fabrication and characterization user facilities.

- 2.2: Improve access for the academic and small-business research community to flexible design tools and wafer-scale fabrication resources.

- 2.3: Facilitate research access to key functional materials.

- 2.4: Expand access to advanced cyberinfrastructure for modeling and simulation.

- 2.5: Support advanced research, development, and prototyping to bridge the lab-to-fab gap.

- 2.6: Support advanced assembly, packaging, and testing.

### Goal 3. Grow and Sustain the Technical Workforce for the Microelectronics R&D to Manufacturing Ecosystem

- 3.1: Support learners and educators in and across science and technology disciplines relevant to microelectronics.

- 3.2: Foster meaningful public engagement in microelectronics and raise awareness of career opportunities in the semiconductor industry.

- 3.3: Prepare an inclusive current and future microelectronics workforce.

- 3.4: Build and drive microelectronics research and innovation capacity.

### Goal 4. Create a Vibrant Microelectronics Innovation Ecosystem to Accelerate the Transition of R&D to U.S. Industry

- 4.1: Support, build, and bridge centers, public private partnerships, and consortia to deepen collaboration among various stakeholders in the microelectronics ecosystem.

- 4.2: Engage with and leverage the CHIPS Industrial Advisory Committee.

- 4.3: Motivate and align the microelectronics community on key technical challenges with R&D roadmaps and grand challenges.

- 4.4: Facilitate academic, government, and industrial exchange to broaden understanding of needs and opportunities.

- 4.5: Support entrepreneurship, start-ups, and early-stage businesses through targeted programs and investments.

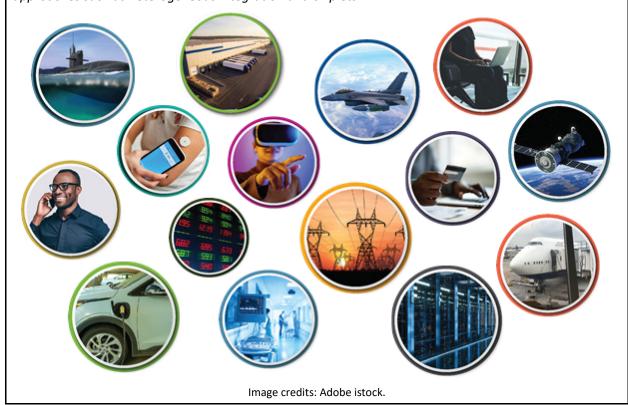

#### Microelectronics have become essential for many aspects of everyday life.

Semiconductors are critical to U.S. economic and national security and have become essential to many aspects of everyday life. Examples depicted here include automotive, health care, aerospace, virtual reality, financial systems, e-commerce, space satellites, defense, energy, computing, agriculture, and telecommunications. As microelectronic devices have become pervasive, their key performance requirements have become increasingly diverse, necessitating a divergence from the traditional scaling in feature size exemplified by Moore's Law. For example, the requirements for satellite applications include proven technologies that are radiation hardened, supercomputers maximize performance and speed, but devices on the edge such as sensors may prioritize low power. These application-specific requirements are driving an increased diversification of microelectronics, which will be enabled and advanced by approaches such as heterogeneous integration and chiplets.

The White House supply chain report emphasized the importance of the semiconductor industry to the U.S. economy, which ranked fifth overall in U.S. export sales in 2022. The federal government is also an important consumer of microelectronics, and it is critical that it has access to trusted and assured microelectronics for essential functions such as communications, navigation, sensing, critical infrastructure, public health, and national security. Microelectronics underpin a wide range of emerging technologies including quantum information sciences, artificial intelligence, advanced wireless networks (6G and beyond), safe and secure health care technologies, and clean-energy and energy-efficient technologies needed to address the climate crisis. 10

State of the U.S. Semiconductor Industry, Semiconductor Industry Association, 2023, <a href="https://www.semiconductors.org/wp-content/uploads/2023/07/SIA\_State-of-Industry-Report\_2023\_Final\_072723.pdf">https://www.semiconductors.org/wp-content/uploads/2023/07/SIA\_State-of-Industry-Report\_2023\_Final\_072723.pdf</a>, p. 23

<sup>&</sup>lt;sup>10</sup> Climate change widespread, rapid, and intensifying, IPCC, <a href="https://www.ipcc.ch/2021/08/09/ar6-wg1-20210809-pr">https://www.ipcc.ch/2021/08/09/ar6-wg1-20210809-pr</a>

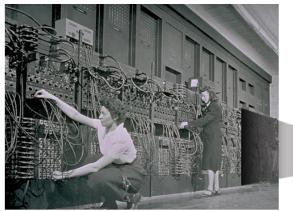

#### ENIAC on a chip

To illustrate the significant changes in size and scale of computing technologies, students designed and built "ENIAC-on-a-chip" to celebrate the  $50^{th}$  anniversary of the first programmable, electronic, general-purpose digital computer called the Electronic Numerical Integrator and Computer (ENIAC). ENIAC was designed under a U.S. Army R&D program and was completed in 1945. ENIAC contained over 18,000 vacuum tubes and was approximately 8 feet tall, 3 feet deep, 100 feet long, and weighed more than 30 tons. ENIAC was programmed by hand using cables and switches, as illustrated in the figure on the left. The image on the right depicts a chip that recreated ENIAC using 0.5  $\mu$ m complementary metal-oxide-semiconductor (CMOS) technology in 1995, replacing the vacuum tubes with transistors. Using today's technology, the chip would be approximately 1,000 times smaller. With respect to performance, ENIAC could do about 500 floating-point operations per second (FLOPS) while the Frontier supercomputer at Oak Ridge National Laboratory can now do more than one quintillion (1,000,000,000,000,000,000) FLOPS.

Image credits: Left—Alamy Stock Photo; Right—Trustees of the University of Pennsylvania, all rights reserved, 1998 (photo by Felice Macera).

It is because of the importance of this industry to the nation's economy and security that the bipartisan CHIPS Act of 2022 (Division A of the CHIPS and Science Act of 2022<sup>12</sup>) was enacted and appropriated more than \$52 billion to grow the nation's semiconductor manufacturing base and accelerate microelectronics R&D. Moreover, several recent reports have emphasized the importance of the industry. For example, in a 2018 assessment, the Department of Defense (DOD) identified threats to the microelectronics supply chain as well as related R&D and manufacturing issues for multiple critical defense sectors. In 2020–2023, the Congressional Research Service (CRS) examined the technical challenges facing the semiconductor industry, domestic and global supply chains, secure and trusted production of semiconductors for national security, and associated federal policies and research investments, along with possible legislation to address these challenges. The Final Report of the

https://www.seas.upenn.edu/~jan/eniacproj.html

<sup>&</sup>lt;sup>12</sup> CHIPS Act of 2022 (Division A of Public Law 117-167), <a href="https://www.congress.gov/bill/117th-congress/house-bill/4346/text:https://www.congress.gov/bill/117th-congress/house-bill/4346">https://www.congress.gov/bill/117th-congress/house-bill/4346</a>

Assessing and Strengthening the Manufacturing and Defense Industrial Base and Supply Chain Resiliency of the United States, DOD, 2018, <a href="https://media.defense.gov/2018/oct/05/2002048904/-1/-1/1/assessing-and-strengthening-the-manufacturing-and%20defense-industrial-base-and-supply-chain-resiliency.pdf">https://media.defense.gov/2018/oct/05/2002048904/-1/-1/1/assessing-and-strengthening-the-manufacturing-and%20defense-industrial-base-and-supply-chain-resiliency.pdf</a>

See: Semiconductors: U.S. Industry, Global Competition, and Federal Policy, Congressional Research Service, 2020, <a href="https://crsreports.congress.gov/product/pdf/R/R46581">https://crsreports.congress.gov/product/pdf/R/R46581</a>; Semiconductors, CHIPS for America, and Appropriations in the U.S. Innovation and Competition Act (S. 1260), Congressional Research Service, 2022, <a href="https://crsreports.congress.gov/product/pdf/IF/IF12016">https://crsreports.congress.gov/product/pdf/IF/IF12016</a>; Semiconductors and the Semiconductor Industry, <a href="https://crsreports.congress.gov/product/pdf/R/R47508">https://crsreports.congress.gov/product/pdf/R/R47508</a>; Frequently Asked Questions: CHIPS Act of 2022 Provisions and

National Security Commission on Artificial Intelligence (AI) identified domestically-located semiconductor fabs as a requirement to maintain the nation's leadership in AI. <sup>15</sup> Semiconductors and microelectronics were also identified as areas of particular importance to the national security of the United States in the updated Critical and Emerging Technologies List. <sup>16</sup>

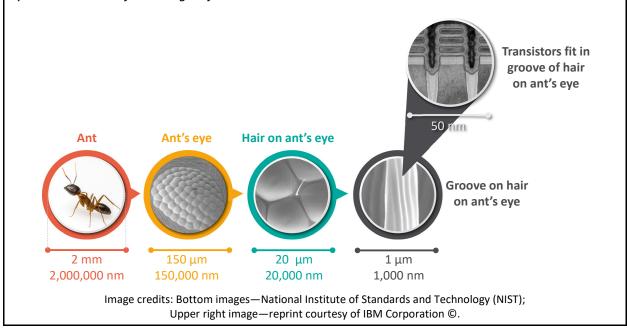

#### Just how small is a transistor?

The following images show the size of transistors compared to an ant. The diameter of the circle around the picture of the ant depicts 2 millimeters (mm), or 0.002 meters. The next image is a picture taken in a scanning electron microscope (SEM) of an ant's eye, about 150 micrometers ( $\mu$ m), or 0.00015 meters in diameter. The third image is a picture of a hair on the ant's eye. The circle is 20  $\mu$ m across. The fourth picture is a close-up SEM image of the hair, showing grooves on the hair. The diameter is 1  $\mu$ m (or one thousand nanometers [nm]). A cross-section of integrated circuit transistors is shown in the top electron microscope image, illustrating modern integrated circuit transistors fit into a groove of the hair on an ant's eye. The diameter of this image is just 50 nm.

Microelectronics R&D is essential to continue advancing technology and systems, and to realize the long-term goal of strengthening domestic manufacturing and mitigating supply chain risks. Additionally, input from federal Requests for Information (RFIs),<sup>17</sup> recommendations from the

Implementation, <a href="https://crsreports.congress.gov/product/pdf/R/R47523">https://crsreports.congress.gov/product/pdf/R/R47523</a>; Semiconductors and the CHIPS Act: The Global Context, Congressional Research Service, 2023, <a href="https://crsreports.congress.gov/product/pdf/R/R47558">https://crsreports.congress.gov/product/pdf/R/R47558</a>.

<sup>&</sup>lt;sup>15</sup> See Chapter 13 of *Final Report*, National Security Commission on Artificial Intelligence, 2021, <a href="https://www.nscai.gov/wp-content/uploads/2021/03/Full-Report-Digital-1.pdf">https://www.nscai.gov/wp-content/uploads/2021/03/Full-Report-Digital-1.pdf</a>.

https://www.whitehouse.gov/wp-content/uploads/2022/02/02-2022-Critical-and-Emerging-Technologies-List-Update.pdf

Relevant RFIs include Current and Future Workforce Needs to Support a Strong Domestic Semiconductor Industry, NIST, DOC, 2018, <a href="https://www.federalregister.gov/documents/2018/07/16/2018-15077/current-and-future-workforce-needs-to-support-a-strong-domestic-semiconductor-industry">https://www.federalregister.gov/documents/2018/07/16/2018-15077/current-and-future-workforce-needs-to-support-a-strong-domestic-semiconductor-industry</a>; National Nanotechnology Initiative Strategic Planning, OSTP, 2020, <a href="https://www.federalregister.gov/documents/2020/10/13/2020-22556/request-for-information-national-nanotechnology-initiative-strategic-planning">https://www.federalregister.gov/documents/2020/10/13/2020-22556/request-for-information-national-nanotechnology-initiative-strategic-planning</a>; Microelectronics R&D Facility Capabilities for Prototyping, DOD, 2020, <a href="https://sam.gov/opp/eaf0eb36b54542b28c6ee88252e9f4b0/view">https://sam.gov/opp/eaf0eb36b54542b28c6ee88252e9f4b0/view</a>; Basic Research Initiative for Microelectronics, Office of Science, DOE, 2019, <a href="https://www.federalregister.gov/documents/2019/07/12/2019-14869/request-for-information-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-planning-to-mation-basic-

stakeholder community, and multiple other reports from the public and private sectors, <sup>18,19</sup> make it clear that a strong, innovative domestic R&D effort is vital to future U.S. competitiveness and security. Taken all together, a set of key R&D trends and opportunities emerge from these resources:

- The diversity of devices and their applications continues to grow beyond conventional processors and memory, requiring innovation throughout the generation, communication, storage, and processing of data across many scales and types of information systems.

- Microelectronics technology is critical to fields beyond information technology, with tremendous growth expected in areas such as power management, medical devices, and sensing.

- A comprehensive approach to R&D across the "full stack" provides an opportunity to

achieve performance, reliability, and security improvements in devices and systems.

Although much attention is focused on the design and scaling of foundational devices, there are

also major challenges ahead for fabrication, metrology, testing, verification and validation,

heterogeneous integration, and advanced packaging. Moreover, challenges are not limited to

hardware: advances in devices, design and manufacturing, circuits, and systems integration

require concomitant innovations across the computer architecture, software, and application

layers.

- Integrated design offers an approach to accelerate innovation. In addition, it can ensure that critical system attributes are captured from the start and considered throughout the development cycle, including performance, reliability, energy efficiency, and security.

- The U.S. microelectronics research ecosystem continues to excel at basic and early-stage applied research, but additional investment in domestic infrastructure, a renewed emphasis on manufacturing science and engineering, and an agile workforce are needed to efficiently transition innovations to industry.

- Affordable and rapid access to design and prototyping capabilities will increasingly enable domestic innovations to transition more rapidly from R&D into manufacturing.

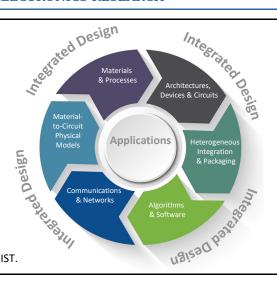

#### What is "the stack"?

Throughout this report, the "stack" or "full stack" refers to the full range of science and technology elements required to make up a complete microelectronics system shown in the figure at right, from the most basic levels of hardware (e.g., materials and

circuits) all the way through the high-level software and the applications where it will be used. (Background image is a cross section of a state-of-the-art chip. Image credit: NIST.)

<sup>&</sup>lt;u>research-initiative-for-microelectronics</u>; and *Draft National Strategy on Microelectronics Research*, OSTP, 2022, <a href="https://www.federalregister.gov/documents/2022/09/15/2022-19935/request-for-information-draft-national-strategy-on-microelectronics-research">https://www.federalregister.gov/documents/2022/09/15/2022-19935/request-for-information-draft-national-strategy-on-microelectronics-research</a>.

Public sector reports include Basic Research Needs for Microelectronics, DOE, 2018, <a href="https://www.osti.gov/biblio/1545772">https://www.osti.gov/biblio/1545772</a>; Semiconductor Foundry Access by U.S. Academic Researchers in Micro- and Nano- Circuits and Systems, NSF, 2021, <a href="https://nsfedaworkshop.nd.edu/assets/429148/nsf20">https://nsfedaworkshop.nd.edu/assets/429148/nsf20</a> foundry meeting report.pdf; and Report of the first DOE\AMO Workshop on Semiconductor RDD&D for Energy Efficiency, DOE, 2021, <a href="https://www.energy.gov/eere/amo/articles/amo-semiconductor-workshop-integrated-sensor-systems-report">https://www.energy.gov/eere/amo-systems-report</a>. In addition, summaries of other AMO workshops in this series can be found at <a href="https://www.energy.gov/eere/ammto/resource-library">https://www.energy.gov/eere/ammto/resource-library</a>.

Private sector reports include, for example, Semiconductor Research Opportunities: An Industry Vision and Guide, Semiconductor Industry Association (SIA), 2017, <a href="https://www.semiconductors.org/wp-content/uploads/2018/06/SIA-SRC-Vision-Report-3.30.17.pdf">https://www.semiconductors.org/wp-content/uploads/2018/06/SIA-SRC-Vision-Report-3.30.17.pdf</a>; Chipping In:, SIA, 2021, <a href="https://www.semiconductors.org/wp-content/uploads/2021/05/SIA-Impact\_May2021-FINAL-May-19-2021\_2.pdf">https://www.semiconductors.org/wp-content/uploads/2021/05/SIA-Impact\_May2021-FINAL-May-19-2021\_2.pdf</a>; The Decadal Plan for Semiconductors, Semiconductor Research Corporation, 2021, <a href="https://www.src.org/about/decadal-plan">https://www.src.org/about/decadal-plan</a>, and An Analysis of the North American Semiconductor and Advanced Packaging Ecosystem, IPC, 2021, <a href="https://emails.ipc.org/links/IPCadvpack-ecosystem-report-final.pdf">https://emails.ipc.org/links/IPCadvpack-ecosystem-report-final.pdf</a>.

Capabilities are needed from the device scale to the wafer scale, both near or at leading-edge process nodes, as well as at the more mature nodes important for analog and non-silicon technologies. Students and researchers need access to these capabilities for experiential workforce training.

- Access to well-prepared talent is a significant challenge across the entire value chain and

will require both short-term and long-term solutions. Welcoming pathways are needed to make

the United States a magnet for outstanding foreign talent in high-demand fields. Improvements

in both curriculum and outreach are needed to develop and expand the equitable, inclusive,

and diverse domestic science, technology, engineering, and mathematics (STEM) talent pool to

support microelectronics R&D and the semiconductor industry.

- Strong engagement with allies and partners is required to ensure the success of the entire innovation ecosystem. The semiconductor industry is global; no nation can bring together the technology, supply chains, and expertise to support leading-edge R&D and manufacturing alone. Tech diplomacy will be an important tool to engage allies and partners.

- Improving the energy efficiency of microelectronics is increasingly essential for sustainability. Rapid growth in microelectronics use and the simultaneous slowing of energy efficiency improvements are creating new economic and environmental risks. To reduce these risks, microelectronics R&D investments must include a focus on energy efficiency and on full-life-cycle sustainability, including reducing the use of materials that are scarce or hazardous to the environment.

- Safeguarding intellectual property is essential to ensure that U.S. industry captures economic benefit to sustain private R&D investments. Key intellectual property developed by and within the United States must be protected, while also improving the ability to appropriately share information among collaborative efforts. Applied research is intended to provide technical discriminators giving microelectronics manufacturers a strategic advantage in the marketplace. Safeguards (i.e., cybersecurity, intellectual property enforcement, etc.) must be implemented and effectively enforced to ensure that key innovations are not inadvertently or inappropriately infringed upon.

These trends and opportunities have informed the goals, needs, and strategies presented in this document to accelerate the pace of innovation and translation through collaborative research, access to advanced infrastructure, and a culture of co-design across the microelectronics R&D enterprise. Attention must focus on developing and sustaining a vibrant and connected microelectronics ecosystem to ensure U.S. leadership in this important area.

#### The Microelectronics Innovation Ecosystem

The microelectronics innovation ecosystem is complex and extremely capital-, knowledge-, and R&D-intensive. Industry consolidation has imposed limits on the associated R&D ecosystem. With worldwide manufacturing of leading-edge microelectronics now dependent on only a handful of companies, the opportunity for researchers to exploit advanced processes is limited. Researchers in academia, government, and industry who do not require high-volume production have limited access to the capabilities needed for advancing the R&D frontier, significantly constraining their ability to develop and transition innovations to leading-edge manufacturing. Limited access to leading-edge

For example, see Measuring distortions in international markets: The semiconductor value chain, OECD, 2019, <a href="https://www.oecd-ilibrary.org/trade/measuring-distortions-in-international-markets\_8fe4491d-en">https://www.oecd-ilibrary.org/trade/measuring-distortions-in-international-markets\_8fe4491d-en</a>; and Strengthening the Global Semiconductor Supply Chain in an Uncertain Era, Boston Consulting Group and the Semiconductor Industry Association, 2021, <a href="https://www.semiconductors.org/strengthening-the-global-semiconductor-supply-chain-in-an-uncertain-era">https://www.semiconductors.org/strengthening-the-global-semiconductor-supply-chain-in-an-uncertain-era</a>.

capabilities also restricts opportunities to provide experiential training for workforce development. CHIPS Act investments aim to address these issues.

Beyond the leading edge of current CMOS technology, the microelectronics industry is facing profound changes associated with the accelerated pace of innovation and an explosion in the diversity of technologies emerging from academia, Department of Energy (DOE) National Laboratories and other Federally Funded Research and Development Centers (FFRDCs), nonprofit laboratories, government facilities, and companies small and large. Effective pathways for transitioning new research advances into applications need to be established and strengthened to ensure that the United States captures the benefits from R&D investments and that key intellectual property (IP) is available for domestic manufacturing. Additionally, as new challenges are identified in manufacturing, these technical needs must be communicated back to the research community.

As part of the national R&D ecosystem, over 20 federal agencies fund R&D, with the nature of the activities determined by the mission of each agency. The Department of Commerce (DOC), National Aeronautics and Space Administration (NASA), National Science Foundation (NSF), Department of Homeland Security (DHS), Department of Health and Human Services (HHS), DOD, DOE, and other federal agencies support both intramural R&D (conducted within government facilities and DOE National Laboratories) and extramural R&D (conducted by academia, industry, and other organizations through grants, contracts, and other agreements). The wide span of R&D activities supported by federal research funding requires that IP developed is protected from unintentional, forced, or coerced technology transfer. Agencies also support workforce development across all educational levels through a variety of mechanisms, including support for formal and informal learning, internships, and fellowships; curriculum development; and coordinated efforts to broaden participation in STEM. While each agency has mission-oriented priorities determining the focus of its microelectronics-related research, as discussed below and throughout this strategy, there are multiple interagency mechanisms in place to coordinate R&D priorities and programs and to ensure that the outcomes of research are shared for mutual benefit.

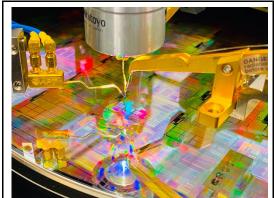

Within the microelectronics innovation ecosystem, an important element of federal funding is support for infrastructure along the technology development pathway. For early-stage research, many facilities exist in academic institutions, government facilities, and DOE National Laboratories and other FFRDCs, particularly for the fabrication and characterization of materials and devices. Another area of federal investment is in cyber infrastructure, including modeling, simulation, and data. Several user facility networks connected to the National Nanotechnology Initiative (NNI)<sup>22</sup> provide researchers from academia, industry, and government with access to suites of tools and scientific expertise that support microelectronics R&D. These facilities have vastly broadened participation of researchers from small businesses and institutions that would not be able to purchase the equipment on their own. This has helped democratize innovation that requires specialized facilities and equipment, especially for semiconductor R&D and fabrication.

Once proofs of concepts at the device level are achieved, innovation often becomes hindered in the current U.S. ecosystem by a lack of access to the necessary advanced development capabilities. Investments in domestic materials supply, design, fabrication, and packaging capabilities are required to address this laboratory-to-fabrication (lab-to-fab) gap. Investments are required to enable and sustain advanced prototyping and scale-up of new devices and architectures, along with the associated manufacturing and metrology instrumentation, and in concert with the required design of software and

<sup>&</sup>lt;sup>21</sup> See Research and Development chapter of *Analytical Perspectives: Budget of the U.S. Government, Fiscal Year 2024:* https://www.whitehouse.gov/wp-content/uploads/2023/03/ap\_6\_research\_fy2024.pdf.

<sup>22</sup> https://www.nano.gov/userfacilities

#### NATIONAL STRATEGY ON MICROELECTRONICS RESEARCH

applications. Moreover, access to these capabilities by both researchers and students will provide hands-on experiential training to expand the domestic microelectronics workforce.

The CHIPS for America Act of 2021<sup>23</sup> authorized multiple programs to help bridge this lab-to-fab gap, while the CHIPS Act of 2022<sup>24</sup> appropriated funding for the programs. Section 9903 of the CHIPS for America Act of 2021 authorizes DOD to establish a National Network for Microelectronics Research and Development to enable the lab-to-fab transition of microelectronics innovations in the United States. Section 9906 directs DOC to establish a National Semiconductor Technology Center to conduct research and prototyping of advanced semiconductor technologies; a microelectronics research program at NIST to conduct semiconductor metrology research and development; a National Advanced Packaging Manufacturing Program to strengthen semiconductor advanced test, assembly, and packaging capabilities; and up to three Manufacturing USA institutes focused on semiconductor manufacturing.

Within the broader U.S. R&D ecosystem, there are many regional innovation hubs around the country composed of industry clusters complemented by federally supported academic centers, often focused on specific technologies and/or local research strengths. These local hubs are valuable national resources, and ensuring that they are well coupled to other elements of the overall R&D ecosystem, including microelectronics, will strengthen the national innovation base.

The U.S. semiconductor industry invests heavily in R&D efforts, estimated to be nearly \$60 billion in 2022. For maintain their world-leading expenditures on R&D, U.S. companies must have access to foreign markets where they can compete and win based on superior technology. Trade policy must protect U.S. companies from discrimination in global markets. Collaboration and alignment with allies and partners will help address national security concerns and help U.S. companies hold their ground in the intense global competition for technology leadership.

The White House and federal departments and agencies recognize that openness is a foundation for R&D leadership and that international talent flow is critical to the success of the global enterprise. <sup>26,27</sup> However, as made clear in Guidance for Implementing National Security Presidential Memorandum 33 (NSPM-33), <sup>28</sup> the U.S. government and its partners must strengthen protections of R&D against foreign government interference and exploitation, diligently safeguarding intellectual capital and property. Protections may include improved, risk-based processes for evaluating research partnerships and proposed foreign investments; active participation of U.S. experts in international standards organizations; closer coordination with international partners on research security; and a campaign of outreach and education on the importance of this topic across the microelectronics R&D community. <sup>29</sup>

William M. (Mac) Thornberry National Defense Authorization Act for Fiscal Year 2021, (Public Law 116-283), Title XCIX ("Creating Helpful Incentives to Produce Semiconductors (CHIPS) for America") (herein "CHIPS for America Act of 2021")

<sup>&</sup>lt;sup>24</sup> CHIPS Act of 2022 (Division A of Public Law 117-167), <a href="https://www.congress.gov/bill/117th-congress/house-bill/4346/text">https://www.congress.gov/bill/117th-congress/house-bill/4346/text</a>: <a href="https://www.congress.gov/bill/117th-congress/house-bill/4346">https://www.congress.gov/bill/117th-congress/house-bill/4346/text</a>: <a href="https://www.congress.gov/bill/117th-congress/house-bill/4346">https://www.congress.gov/bill/117th-congress/house-bill/4346</a>

State of the U.S. Semiconductor Industry, Semiconductor Industry Association, 2023, <a href="https://www.semiconductors.org/wp-content/uploads/2023/07/SIA\_State-of-Industry-Report\_2023\_Final\_072723.pdf">https://www.semiconductors.org/wp-content/uploads/2023/07/SIA\_State-of-Industry-Report\_2023\_Final\_072723.pdf</a>, p. 21

https://www.quantum.gov/wp-content/uploads/2021/10/2021\_NSTC\_ESIX\_INTL\_TALENT\_QIS.pdf

https://www.whitehouse.gov/briefing-room/statements-releases/2022/01/21/fact-sheet-biden-harris-administration-actions-to-attract-stem-talent-and-strengthen-our-economy-and-competitiveness/.

Guidance For Implementing National Security Presidential Memorandum 33 (NSPM-33) On National Security Strategy For United States Government-Supported Research And Development, <a href="https://www.whitehouse.gov/wp-content/uploads/2022/01/010422-NSPM-33-Implementation-Guidance.pdf">https://www.whitehouse.gov/wp-content/uploads/2022/01/010422-NSPM-33-Implementation-Guidance.pdf</a>

<sup>&</sup>lt;sup>29</sup> United States Government National Standards Strategy for Critical and Emerging Technology, White House, 2023, <a href="https://www.whitehouse.gov/wp-content/uploads/2023/05/US-Gov-National-Standards-Strategy-2023.pdf">https://www.whitehouse.gov/wp-content/uploads/2023/05/US-Gov-National-Standards-Strategy-2023.pdf</a>

#### A Whole-of-Government Approach

Recognizing the critical role of microelectronics to our health, environment, economy, and national security, a whole-of-government effort is underway to sustain and advance global leadership by the United States and its allies in this important field. On August 25, 2022, President Biden released an Executive Order on the Implementation of the CHIPS Act of 2022 that identified implementation priorities and established the CHIPS Implementation Steering Council to coordinate policy development to ensure the effective implementation of the Act within the Executive Branch.<sup>30</sup> Cochaired by the directors of the White House Office of Science and Technology Policy (OSTP), National Security Council (NSC), and National Economic Council (NEC), the steering council includes secretaries from the departments of State, Treasury, Defense, Commerce, Labor, and Energy; the Director of the Office of Management and Budget (OMB); the Administrator of the Small Business Administration; the Director of National Intelligence; the Assistant to the President for Domestic Policy; the Chair of the Council of Economic Advisers; the National Cyber Director; the Director of the National Science Foundation, and the Director of the National Institute of Standards and Technology. This council ensures awareness of ongoing efforts and investments across the government and coordinates policy development at the Cabinet level.

In accordance with Section 9906(a) of the William Mac Thornberry National Defense Authorization Act for Fiscal Year 2021, OSTP established the Subcommittee on Microelectronics Leadership (SML) under the National Science and Technology Council. The Subcommittee membership includes the Department of Commerce, the Department of Defense, the Department of Energy, the Department of Health and Human Services, the National Science Foundation, the State Department, the Department of Homeland Security, and the Office of the Director for National Intelligence. White House components represented include OSTP, OMB, NEC, NSC, and the Office of the U.S. Trade Representative.

Also pursuant to Section 9906(a), the Subcommittee is responsible for developing this National Strategy on Microelectronics Research; for coordinating microelectronics-related research, development, manufacturing, and supply chain security activities and budgets of federal agencies; and for ensuring that such activities are consistent with the strategy. As the body responsible for coordinating microelectronics efforts for the next decade, the SML is developing the structural framework and activities to best serve this role, including the establishment of working groups focused on education and workforce development, and on international engagement. The participating agencies are utilizing their respective authorities to advance R&D and promote policies to support U.S. industry, protect intellectual property, and ensure domestic access to secure microelectronics. Agencies are also collaboratively supporting activities to improve STEM education and increase participation in STEM fields, and to train and expand the microelectronics workforce at all levels. The federal government is engaging and collaborating with allies and partners to strengthen the global microelectronics innovation ecosystem and secure supply chains. Coordinated through the White House, these efforts will not only fuel new research advances to drive microelectronics innovation, but will also help these advances transition to manufacturing and provide good-paying jobs to people across all of America.

As detailed in the sections below, the White House and federal departments and agencies will work together and with academia, industry, nonprofits, and international allies and partners to fuel research advances for future generations of microelectronics; establish best practices to ensure efficient,

https://www.whitehouse.gov/briefing-room/presidential-actions/2022/08/25/executive-order-on-the-implementation-of-the-chips-act-of-2022/

accountable R&D execution; support and connect the microelectronics research infrastructure; expand, train, and support a diverse workforce; and facilitate the rapid transition of R&D to industry.<sup>31</sup>

# Goal 1. Enable and Accelerate Research Advances for Future Generations of Microelectronics

R&D supported by the federal government has been instrumental in laying the foundation for advances in microelectronics and in educating the research and skilled technical workforce needed for design, manufacturing, and application development. The increasing diversity of microelectronics technology and pace of innovation, combined with the growing risks to the global manufacturing and supply chain, requires a renewed federal focus on R&D investment in ways that will alter these trajectories and ensure the future health, economic leadership, and security of the nation. Success requires strategies that engage all sectors of the R&D ecosystem and leverage education, workforce, manufacturing, trade, and regional economic development efforts and policies. Federal agencies, in collaboration with industry, academia, and partners and allies, must work together to accelerate the pace of innovation and translation through collaborative research, access to advanced infrastructure, and a culture of codesign across the microelectronics R&D enterprise.

The past six decades have seen incredible progress in computational power and energy efficiency, enabled in part by continued miniaturization (supported by concomitant advances in materials, design, metrology, and manufacturing). However, this trend in transistor scaling cannot continue indefinitely as the smallest device feature sizes approach the atomic scale. Furthermore, there are emerging applications that will require heterogeneous devices and materials. The semiconductor industry has therefore entered a period of rapid and profound change, and one in which performance advances can no longer be sustained solely by continued miniaturization of silicon-based devices.

#### For example:

- The explosion of data and the emergence of artificial intelligence enabled by machine learning (ML) is driving the development of "compute-in-memory" and other novel memory-intensive and memory-centric architectures that promise to overcome the "von Neumann bottleneck" the energy inefficiency and high latency caused by shuttling data back and forth between separate memory and compute elements.

- As intrachip and interchip data rates have increased, photonic interconnects, previously only

used in long-haul links over optical fiber, are being integrated with electronics in advanced

packaging to move data efficiently.

- Advances in materials and devices are enabling ultra-high-frequency free-space communication using mm-wave and THz systems.

- Advanced photonics are poised to deliver dedicated artificial intelligence/machine learning (AI/ML) hardware that operates at low power and extraordinary speed.

Many aspects of microelectronics R&D intersect with other initiatives and Biden-Harris Administration priorities, including the National Nanotechnology Initiative, the Future Advanced Computing Ecosystem (formerly the National Strategic Computing Initiative), the National Quantum Initiative, and the Networking and Information Technology Research and Development (NITRD) Program. SML is working with all of these efforts to ensure synergy and coordination.

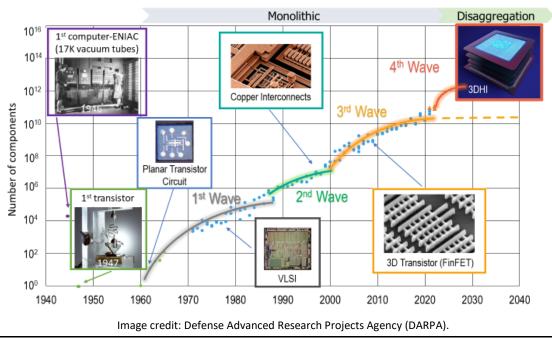

#### Dramatic progress in scaling of microelectronic devices since the first digital computers

This graph illustrates the change in the number of components on an integrated circuit, or chip, over time, along with some of the technological innovations that enabled the different waves of progress. For reference, the first programmable, electronic, general-purpose digital computer, ENIAC, built using vacuum tubes, is the first point in 1945. (See more about ENIAC in the call-out on p. 4.) The first transistor, made from germanium, was invented in 1947 and was approximately 1 cm long. The first silicon transistor came a few years later. The first silicon integrated circuit was demonstrated in late 1959. With the invention of the first metal-oxide-semiconductor field effect transistor (MOSFET) integrated circuit in the early 1960s, the number of components began to increase exponentially. Each time progress slowed, advances in manufacturing science, materials, and device design re-energized the field. In the first wave, shrinking the size of the transistor, the basic building block of these chips, led directly to dramatic increases in the number of components on a chip and dramatic reductions in the cost per transistor—the observation that formed the basis for Moore's Law. The original planar integrated circuit went from small-scale integration (SSI) to medium-scale integration (MSI) to large-scale integration (LSI) to very large-scale integration (VLSI). During the second wave, the introduction of new materials, including the transition from aluminum to copper interconnects, resulted in better speed, power, and reliability, and enabled further reduction in transistor size. The third wave began with the transition from planar to three dimensional (3D) transistors using fin field-effect transistors (FinFETs), resulting in additional performance gains and continued miniaturization. As the technologies for shrinking the size of the transistors, which are now only a few atoms across, reach their physical limits, new strategies are required. We are at the start of the "4th wave of microelectronics," leaving behind device scaling and entering into an age where higher performance will be driven by innovations in the integration of heterogeneous technologies and 3D devices. While efforts continue to decrease transistor size, new tools, manufacturing methods, and circuit architectures must be developed to deliver continued progress.

- A revolution is underway in electronic design automation (EDA), including the application of AI/ML, cloud-based platforms, and design-technology co-optimization (DTCO) that will make it feasible for designers to create ever-more-complex integrated circuits, optimized for almost every conceivable application, faster and more reliably. These circuits will deliver tremendous gains in speed and efficiency and affect the performance of every information technology sector, from data centers to edge computing and the internet of things (IoT).

- Heterogeneous and domain-specific computing architectures that optimize performance for specific applications are being deployed to accelerate time-to-solution.

- Microelectromechanical systems (MEMS) are becoming increasingly sophisticated and powerful as they are integrated with processing and intelligence.

- Progress is being made in integrating semiconductor systems with biomolecular, biological, neuromorphic, and bio-inspired systems that may one day deliver unprecedented improvements in energy efficiency and other unique capabilities in computation, AI, robotics, sensing, and health care beyond the potential of either domain on its own.

- As the demands for different applications diverge, extreme reliability and operation at cryogenic temperatures, high temperatures, or low power will modify the standard metrics of power, performance, area, and cost driving the development of new devices, architectures, and algorithms.

- As electronics move towards more heterogeneous architectures, performance metrics become

more complex. Heterogeneous integration—the science and technology of bringing disparate

materials, devices, and circuits together to create highly functional, high-performance

systems—is key to enabling continued progress. However, as more and more diverse

components are integrated, the physical, electronic, optical, and software challenges of

making them operate seamlessly together become more complex.

- Dramatic increases in system heterogeneity and complexity also call for R&D attention on design flows that prioritize security and reliability, and that integrate both formal and empirical verification and validation throughout the full design, fabrication, and manufacturing process.

As referenced in the introduction, there are calls to not only support the underlying science and engineering that shape and drive microelectronics, including computer science, computing architectures, physics, chemistry, and materials science, but also to widely embrace the principles of integrated design where these different aspects of research inform and guide each other synergistically, and with sustainable development in mind. Open communication between all levels of the stack is essential to ensure that end-use capabilities and requirements inform research, and that research breakthroughs are rapidly incorporated into development efforts. Such an integrated approach is the only way to guarantee that critical system attributes such as security, reliability, and radiation-hardness<sup>32</sup> are designed in from the start and considered throughout the development cycle. Lastly, with the projected increase in resources needed to produce, operate, and eventually recycle microelectronics systems, a comprehensive approach to estimating total lifetime energy consumption and cost will need input and expertise from across the entire supply chain to identify opportunities to develop more efficient architectures and processes.

-13-

<sup>&</sup>lt;sup>32</sup> Some space, energy, and defense applications require electronics that must function when subjected to a range of radiation sources, including cosmic rays. Radiation-hardened microelectronics perform critical sensing and computational functions so that these devices work as intended in harsh environments.

#### Integrated design

Integrated design refers to a constant bidirectional flow of information from the top to the bottom of the stack driven by applications. Linking end-user needs to R&D is essential for rapid, focused technological development and deployment of research and development to the market. The figure at right illustrates this bidirectional flow of information among the various levels of the stack: material-to-circuit physical models; materials and processes; architectures, devices, and circuits; heterogeneous integration and packaging; algorithms and software; and communications and networks.

Image credit: NIST.

Future leadership in microelectronics requires industry to overcome significant challenges in device physics and fabrication. Deep innovation is therefore needed to identify and transition novel materials and devices from lab-to-fab to enable continued advances in functionality and performance. Successful establishment of a lab-to-fab pathway will require renewed focus on the intersection between fundamental science and manufacturing technologies. Satisfying the ever-increasing demand for storage, bandwidth, and processing power in information and computing technology (ICT) systems, along with the expected growth in the spectrum of applications beyond ICT, requires research and development from devices to systems, and from design to process technology. Central to this strategy is the need for access to design and fabrication facilities, including those equipped to incorporate unconventional materials and/or processes, often in heterogeneous combination with silicon (Si)-CMOS technologies. Innovations across all levels of the stack need to be fully exploited to enable further progress with complex scalable designs in leading-edge Si-CMOS.

Advances in characterization tools and techniques will also be needed to enable detailed and comprehensive investigations of new materials and designs, and to do so with unprecedented spatial resolution, sensitivity, bandwidth, and throughput. The increasing complexity of circuits and systems, including those operating with signals in and interacting across multiple physical domains, will require complementary, multimodal metrology tools as well as new modeling and simulation capabilities to measure performance and provide the data necessary to support EDA, DTCO, and system technology co-optimization (STCO). As the sophistication of these models grows, they will increasingly inform the development of manufacturing process improvements.

In addition to coordination across the hardware-software stack, coordination is required across the R&D community through synergistic flow of research results to achieve the best outcomes. University and small-business researchers must have access to design tools, fabrication facilities, and related infrastructure in which to test their ideas. Commercial fabrication facilities will benefit from working with early-stage testers of novel technology approaches. Likewise, industry R&D will benefit from the training of an advanced research workforce skilled in these areas and graduating from U.S. universities to join their corporate R&D efforts. An important aspect of this collaboration must be to establish and maintain effective research security measures to prevent R&D activities from creating unintended technology transfer.

Over the next five years, U.S. government R&D efforts will focus on the following objectives:

### 1.1: Accelerate the research and development of materials that provide new capabilities or functional enhancements.